DIPを理解する

DIPはプラグイン方式です。この方式でパッケージ化されたチップは2列のピンを有し、DIP構造のチップソケットに直接溶接するか、同じ数の穴を持つ溶接位置に溶接することができます。PCB基板の穴あけ溶接を実現するのに非常に便利で、マザーボードとの互換性も良好ですが、パッケージ面積と厚さが比較的大きいため、挿抜時にピンが損傷しやすく、信頼性が低くなります。

DIP は最も一般的なプラグイン パッケージであり、その応用範囲には標準ロジック IC、メモリ LSI、マイクロコンピュータ回路などが含まれます。スモール プロファイル パッケージ (SOP) は、SOJ (J タイプ ピン スモール プロファイル パッケージ)、TSOP (薄型スモール プロファイル パッケージ)、VSOP (超スモール プロファイル パッケージ)、SSOP (縮小 SOP)、TSSOP (薄型縮小 SOP)、SOT (スモール プロファイル トランジスタ)、SOIC (スモール プロファイル集積回路) などから派生したものです。

DIPデバイスアセンブリの設計上の欠陥

PCBパッケージの穴がデバイスよりも大きい

PCBのプラグイン穴とパッケージピン穴は、仕様に基づいて製版されます。製版時に穴に銅めっきを施す必要があるため、一般的な公差は±0.075mmです。PCBのパッケージ穴が実機のピンより大きすぎると、デバイスの緩み、錫めっき不足、エア溶接などの品質問題につながります。

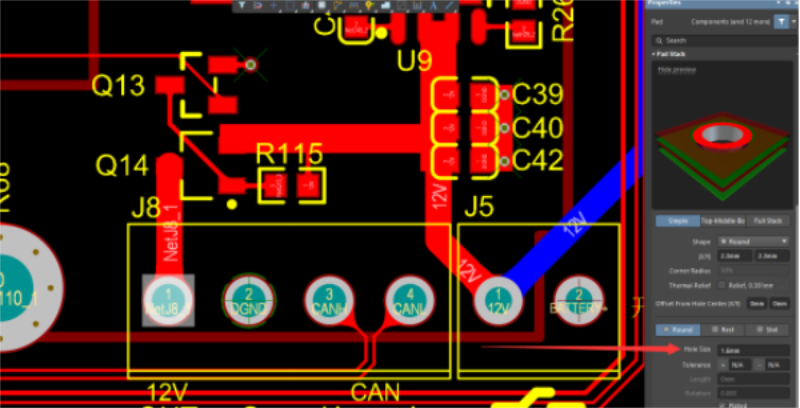

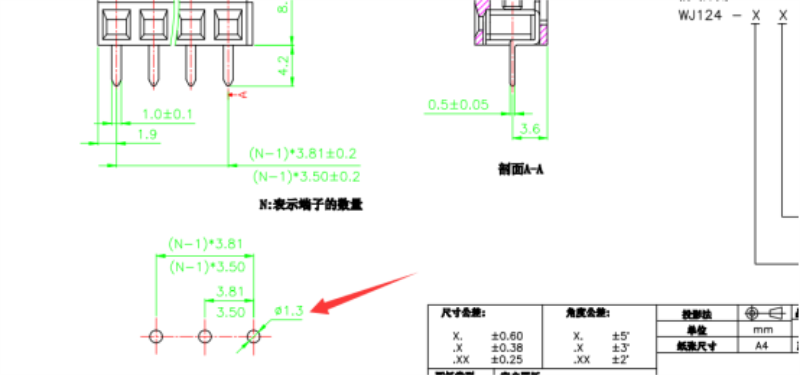

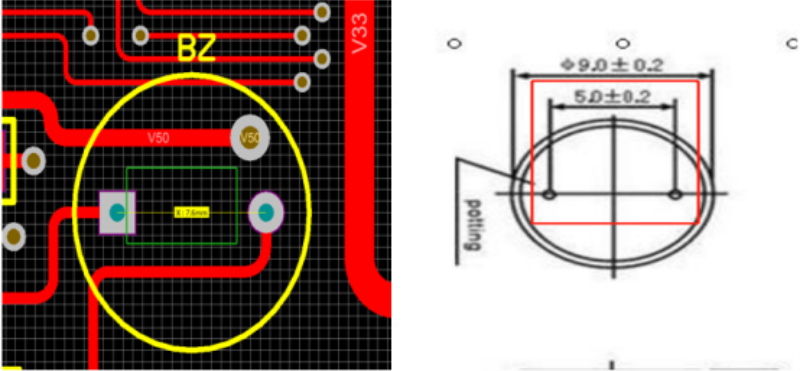

下の図を参照してください。WJ124-3.81-4P_WJ124-3.81-4P (KANGNEX) デバイスのピンは 1.3mm、PCB パッケージの穴は 1.6mm で、開口部が大きすぎると、ウェーブ溶接のスペースタイム溶接が過剰になります。

図に添付されているように、設計要件に従ってWJ124-3.81-4P_WJ124-3.81-4P(KANGNEX)コンポーネントを購入し、ピンは1.3mmが正しいです。

PCBパッケージの穴がデバイスよりも小さい

プラグインですが、穴に銅は入りません。シングルおよびダブルパネルの場合はこの方法を使用できます。シングルおよびダブルパネルは外側に電気伝導があり、はんだで導電性があります。多層ボードのプラグイン穴は小さく、リーミングで内層の伝導を修正できないため、内層に電気伝導がある場合にのみ PCB ボードを作り直すことができます。

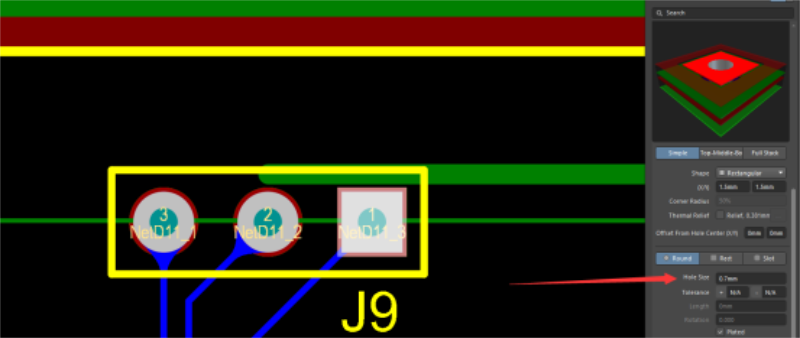

下図に示すように、A2541Hwv-3P_A2541HWV-3P(CJT)の部品は設計要件に従って購入されていますが、ピンは1.0mm、PCBシーリングパッドの穴は0.7mmであるため、挿入に失敗しました。

A2541Hwv-3P_A2541HWV-3P (CJT) の部品は設計要件に従って購入されています。ピンサイズは 1.0mm で問題ありません。

パッケージのピン間隔はデバイスの間隔と異なります

DIPデバイスのPCBシーリングパッドは、ピンと同じ開口部を持つだけでなく、ピン穴間の距離も均一である必要があります。ピン穴とデバイスの間隔が一定でない場合、調整可能な足間隔を持つ部品を除き、デバイスを挿入することはできません。

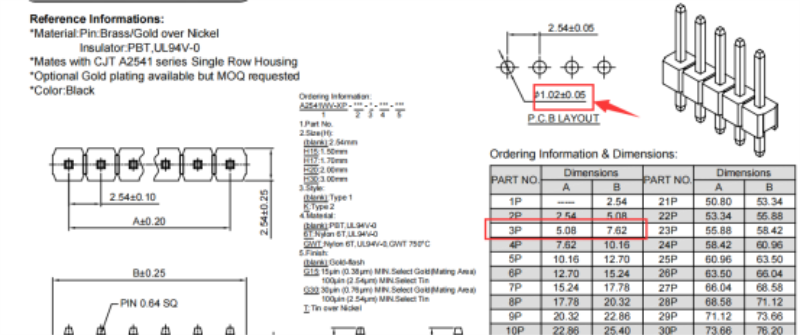

下図に示すように、PCBパッケージのピンホール間隔は7.6mmですが、購入した部品のピンホール間隔は5.0mmです。この2.6mmの差は、デバイスが使用できない原因となります。

PCBのパッケージ穴が近すぎる

PCBの設計、製図、実装においては、ピンホール間の距離に注意を払う必要があります。たとえベアプレートを生成できたとしても、ピンホール間の距離が狭いと、ウェーブはんだ付けによる組み立て時に錫のショートが発生しやすくなります。

下図に示すように、ピン間隔が狭いとショートが発生する可能性があります。はんだ付け時のショートの原因は様々ですが、設計段階で事前に組み立て性を改善できれば、問題の発生率を低減できます。

DIPデバイスのピンの問題例

問題の説明

製品 DIP の波頭溶接後、空気溶接によるネットワーク ソケットの固定足のはんだ板に深刻な錫不足が発生していることが判明しました。

問題の影響

その結果、ネットワークソケットとPCBボードの安定性が悪化し、製品の使用中に信号ピンフットの力が加わり、最終的に信号ピンフットの接続につながり、製品の性能に影響を与え、ユーザーの使用中に故障のリスクが発生します。

問題の拡張

ネットワークソケットの安定性が悪く、信号ピンの接続性能が悪く、品質上の問題があるため、ユーザーにセキュリティリスクをもたらす可能性があり、最終的な損失は想像を絶するものです。

DIPデバイスアセンブリ分析チェック

DIPデバイスのピンに関連する問題は数多くあり、重要なポイントが見落とされやすく、結果として基板が廃棄されてしまうことがあります。では、どうすればこれらの問題を迅速かつ完全に解決できるのでしょうか?

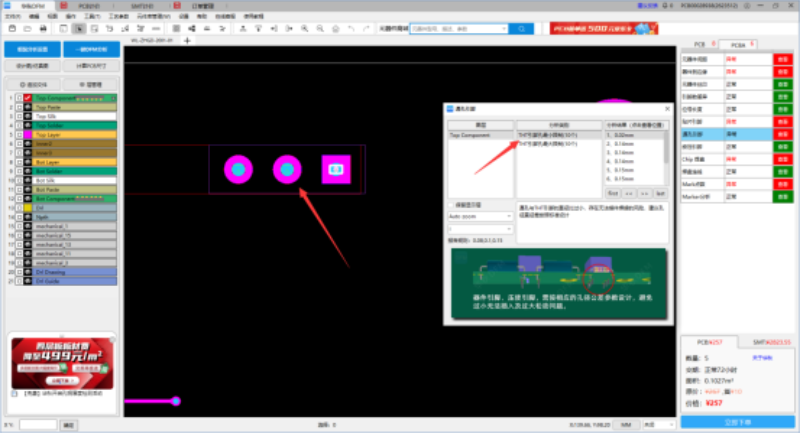

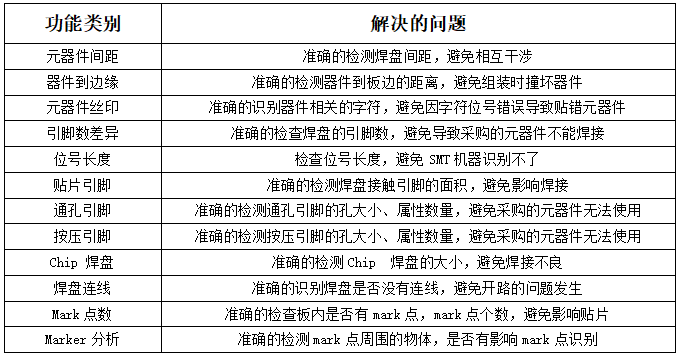

ここで、CHIPSTOCK.TOPソフトウェアのアセンブリおよび解析機能を使用して、DIPデバイスのピンの特殊検査を行うことができます。検査項目には、スルーホールのピン数、THTピンの上限、下限、およびTHTピンの属性が含まれます。ピンの検査項目は、基本的にDIPデバイスの設計において起こり得る問題を網羅しています。

PCB 設計が完了したら、PCBA アセンブリ分析機能を使用して、設計上の欠陥を事前に発見し、生産前に設計上の異常を解決し、アセンブリ プロセスでの設計上の問題、生産時間の遅延、研究開発コストの無駄を回避できます。

アセンブリ解析機能には、10 個の主要項目と 234 個の細目検査ルールがあり、デバイス解析、ピン解析、パッド解析など、考えられるすべてのアセンブリ問題をカバーしており、エンジニアが事前に予測できないさまざまな生産状況を解決できます。

投稿日時: 2023年7月5日