PCB積層設計の2つのルールを理解していますか?

- 1. 各配線層には隣接する参照層 (電源または層) が必要です。

- 2. 隣接する主電源層とグランドは、大きな結合容量を提供するために最小限の距離に保つ必要があります。

以下は 2 層から 8 層のスタックの例です。

- A.片面PCBボードと両面PCBボードの積層

2層の場合は層数が少ないため積層問題はありません。EMI輻射対策は主に配線とレイアウトから考えます。

単層プレートと二層プレートの電磁適合性はますます顕著になってきています。この現象の主な理由は、信号ループの面積が大きすぎるため、強い電磁放射が発生するだけでなく、回路が外部干渉の影響を受けやすくなることです。ラインの電磁両立性を改善する最も簡単な方法は、重要な信号のループ領域を減らすことです。

クリティカル信号: 電磁適合性の観点から、クリティカル信号は主に強い放射線を生成し、外界の影響を受けやすい信号を指します。強い放射線を発生させる可能性のある信号は、通常、クロックやアドレスの低い信号などの周期的な信号です。干渉に敏感な信号は、アナログ信号のレベルが低い信号です。

単層および二層プレートは通常、10KHz 未満の低周波シミュレーション設計で使用されます。

1) 電源ケーブルを同層で放射状に配線し、線路長の合計を最小限に抑えます。

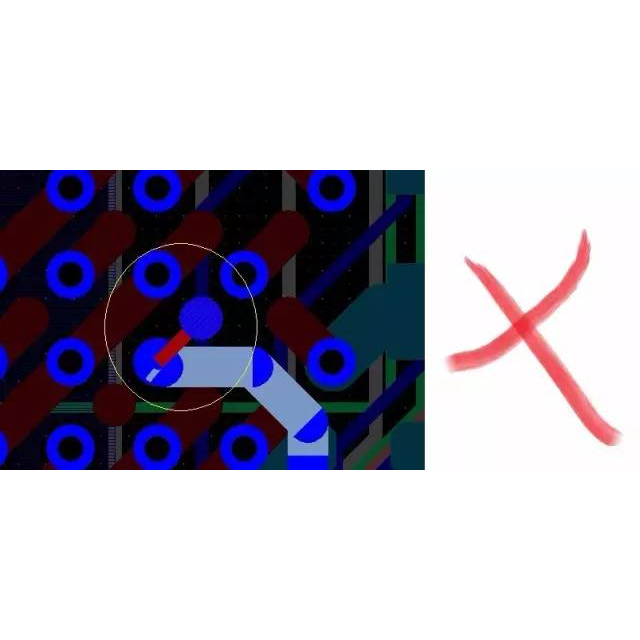

2) 電源線とアース線を近づけるとき。アース線はキー信号線のできるだけ近くに配線してください。したがって、より小さなループ領域が形成され、外部干渉に対する差動モード放射の感度が低下します。信号線の隣にアース線を追加すると、面積が最小の回路が形成され、信号電流は他のアース経路ではなくこの回路を通らなければなりません。

3) 2 層回路基板の場合は、回路基板の反対側、下の信号線の近くに、信号線に沿ってアース線を配置し、できるだけ幅の広い線にすることができます。結果として得られる回路面積は、回路基板の厚さに信号線の長さを乗じたものに等しくなります。

- B. 4層の積層

1. Sig-gnd (PWR)-PWR (GND)-SIG;

2. GND-SIG(PWR)-SIG(PWR)-GND;

これらのラミネート設計の両方で、潜在的な問題は、従来の 1.6 mm (62 ミル) のプレート厚にあります。層間隔が広くなり、インピーダンス、層間結合、シールドの制御に役立つだけでなく、層間の間隔も広くなります。特に、電源層間の間隔が広いとプレート容量が減少し、ノイズフィルタリングに役立ちません。

最初の方式では、通常、ボード上に多数のチップがある場合に使用されます。この方式では SI 性能は向上しますが、EMI 性能はそれほど良くなく、主に配線やその他の詳細によって制御されます。主な注意点: この層は最も高密度の信号層に配置されており、放射線の吸収と抑制に役立ちます。20H ルールを反映するためにプレート面積を増やします。

2 番目の方式では、通常、基板上のチップ密度が十分に低く、必要なパワー銅コーティングを配置するのに十分な領域がチップの周囲にある場合に使用されます。このスキームでは、PCB の外層はすべて層であり、中間の 2 層は信号/電源層です。信号層の電源を太い線路で配線することで、電源電流の経路インピーダンスを低くすることができ、信号マイクロストリップ経路のインピーダンスも低くなり、外部からの内部の信号放射を遮蔽することもできます。層。EMI 制御の観点からは、これは入手可能な最高の 4 層 PCB 構造です。

主な注意点: 中間の 2 つの信号層、電力混合層の間隔は開ける必要があり、ラインの方向は垂直であり、クロストークを避ける必要があります。20H ルールを反映した適切なコントロール パネル領域。ワイヤのインピーダンスを制御する場合は、電源とグランドの銅アイランドの下にワイヤを慎重に配線します。さらに、DC および低周波接続を確保するために、電源または敷設された銅線を可能な限り相互接続する必要があります。

- C. 6層のプレートの積層

高いチップ密度と高いクロック周波数を設計するには、6 層基板の設計を考慮する必要があります。ラミネート方法を推奨します。

1.SIG-GND-SIG-PWR-GND-SIG;

この方式では、信号層が接地層に隣接し、電源層が接地層とペアになった積層方式により良好な信号整合性が実現され、各配線層のインピーダンスを適切に制御でき、両方の層が磁力線を十分に吸収できます。 。さらに、完全な電源供給と形成の条件下で、各信号層により良いリターンパスを提供できます。

2. GND-SIG-GND-PWR-SIG-GND;

この方式の場合、この方式はデバイス密度がそれほど高くない場合にのみ適用されます。この層は上層のすべての利点を備えており、上層と下層のグランドプレーンは比較的完全であり、より優れたシールド層として使用できます。底部プレーンの方がより完全になるため、電源層はメインコンポーネントプレーンではない層の近くに配置する必要があることに注意することが重要です。したがって、EMI 性能は最初の方式よりも優れています。

要約: 6 層基板のスキームでは、良好な電源とグランドの結合を得るために、電源層とグランド間の間隔を最小限に抑える必要があります。しかし、板厚が62milと薄くなり層間隔が狭くなったとはいえ、主電源とグランド層の間隔を非常に小さく制御することは依然として困難です。第1の方式と第2の方式と比較すると、第2の方式のコストは大幅に増加する。したがって、スタックするときは通常、最初のオプションを選択します。設計中は、20H ルールとミラー層ルールに従ってください。

- D. 8層の積層

1、D電磁波吸収能力が低く、電力インピーダンスが大きいため、これは良いラミネート方法ではありません。その構造は次のとおりです。

1.信号1部品表面、マイクロストリップ配線層

2.Signal 2 内部マイクロストリップ配線層、良好な配線層 (X 方向)

3.グランド

4.信号 3 ストリップライン配線層、良好な配線層 (Y 方向)

5.信号 4 ケーブル配線層

6.パワー

7.Signal 5 内部マイクロストリップ配線層

8.信号6マイクロストリップ配線層

2. これは、3 番目のスタッキング モードの変形です。リファレンス層の追加により、EMI性能が向上し、各信号層の特性インピーダンスを適切に制御できます。

1.信号1部品表面、マイクロストリップ配線層、良好な配線層

2.地層、良好な電磁波吸収能力

3.信号 2 ケーブル配線層。優れたケーブル配線層

4.電源層以下の優れた電磁波吸収層を構成 5.グランド層

6.信号 3 ケーブル配線層。優れたケーブル配線層

7.大きな電力インピーダンスを持つ電力形成

8.信号 4 マイクロストリップ ケーブル層。良好なケーブル層

3、T多層グランド基準面の使用は非常に優れた地磁気吸収能力を備えているため、これが最適なスタッキング モードです。

1.信号1部品表面、マイクロストリップ配線層、良好な配線層

2.地層、良好な電磁波吸収能力

3.信号 2 ケーブル配線層。優れたケーブル配線層

4.電源層以下の優れた電磁波吸収層を構成 5.グランド層

6.信号 3 ケーブル配線層。優れたケーブル配線層

7.地層、優れた電磁波吸収能力

8.信号 4 マイクロストリップ ケーブル層。良好なケーブル層

使用する層の数と層の使用方法の選択は、基板上の信号ネットワークの数、デバイス密度、PIN 密度、信号周波数、基板サイズ、その他多くの要因によって異なります。これらの要素を考慮する必要があります。信号ネットワークの数が増えるほど、デバイスの密度が高くなり、PIN の密度が高くなり、可能な限り高い周波数の信号設計を採用する必要があります。EMI 性能を良好にするには、各信号層に独自の基準層があることを確認するのが最善です。