DIP デバイスについて、PCB 関係者の中には、高速ピットを吐き出さない人もいます。

DIPはプラグインです。この方法でパッケージ化されたチップには 2 列のピンがあり、DIP 構造のチップソケットに直接溶接することも、同じ数の穴を備えた溶接位置に溶接することもできます。PCBボードのパーフォレーション溶接を実現するのに非常に便利で、マザーボードとの互換性も良好ですが、実装面積と厚さが比較的大きいため、挿入および取り外しの過程でピンが損傷しやすく、信頼性に劣ります。

DIPは最もポピュラーなプラグインパッケージで、標準ロジックIC、メモリLSI、マイコン回路などを応用範囲としています。 SOJ(J型ピン小型プロファイルパッケージ)から派生した小型プロファイルパッケージ(SOP)、TSOP(薄型小型パッケージ)プロファイルパッケージ)、VSOP(超小型プロファイルパッケージ)、SSOP(縮小SOP)、TSSOP(薄型縮小SOP)およびSOT(小型プロファイルトランジスタ)、SOIC(小型プロファイル集積回路)など。

- PCB パッケージの穴がデバイスより大きい

PCB のプラグイン穴とパッケージのピン穴は仕様に従って描画されます。製版時に穴に銅メッキを施す必要があるため、一般的な公差はプラスまたはマイナス0.075mmです。PCB のパッケージング穴が物理デバイスのピンより大きすぎる場合、デバイスの緩み、錫不足、エア溶接、その他の品質問題が発生します。

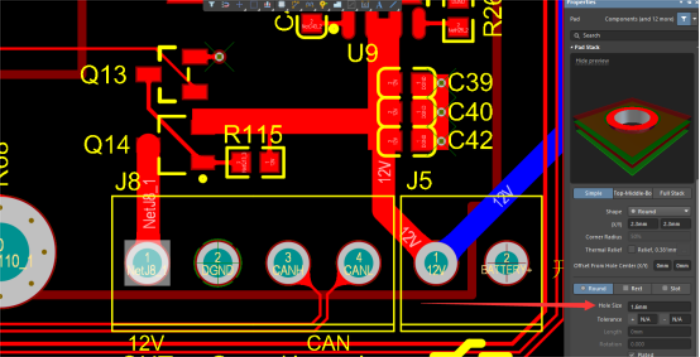

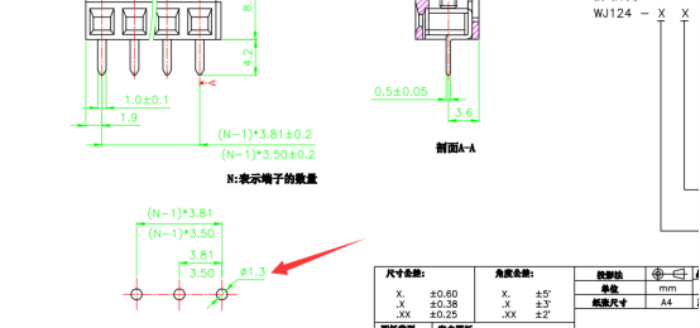

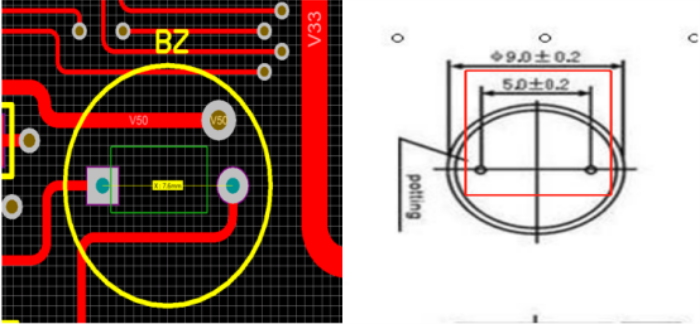

下の図を参照してください。WJ124-3.81-4P_WJ124-3.81-4P (KANGNEX) デバイスピンは 1.3mm、PCB パッケージング穴は 1.6mm、開口部が大きすぎると、オーバーウェーブ溶接のスペースタイム溶接につながります。

図に添付されている、設計要件に従って WJ124-3.81-4P_WJ124-3.81-4P (KANGNEX) コンポーネントを購入してください。ピンは 1.3 mm です。

- PCB パッケージの穴がデバイスより小さい

プラグインですが、銅の穴はありません。シングルパネルとダブルパネルの場合はこの方法を使用できます。シングルパネルとダブルパネルは外部導電性であり、はんだは導電性があります。多層基板はプラグイン穴が小さく、内層の導通はリーマ加工では改善できないため、内層が導通している場合のみPCB基板を作り直すことができます。

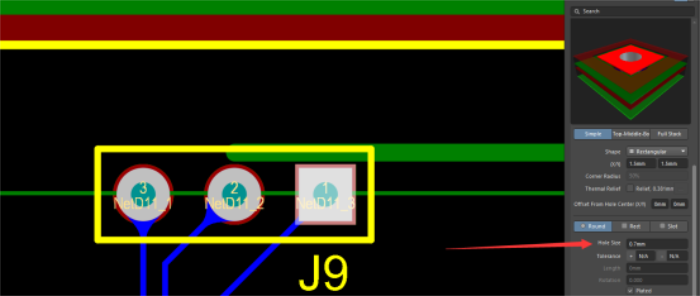

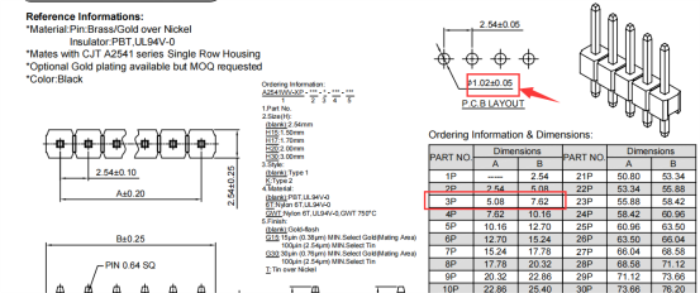

下図に示すように、A2541Hwv-3P_A2541HWV-3P (CJT) のコンポーネントは設計要件に従って購入されます。ピンは1.0mm、PCBシーリングパッドの穴は0.7mmで、挿入に失敗します。

A2541Hwv-3P_A2541HWV-3P (CJT) のコンポーネントは、設計要件に従って購入されます。ピンは1.0mmが正解です。

- パッケージのピン間隔はデバイスの間隔とは異なります

DIP デバイスの PCB シーリング パッドは、ピンと同じ開口部を持つだけでなく、ピン穴間の距離も同じである必要があります。ピン穴とデバイスの間隔が一定していない場合、フット間隔を調整できる部分を除いてデバイスを挿入することはできません。

下図に示すように、PCB パッケージのピンホール距離は 7.6mm、購入した部品のピンホール距離は 5.0mm です。2.6mmの差があると、デバイスは使用できなくなります。

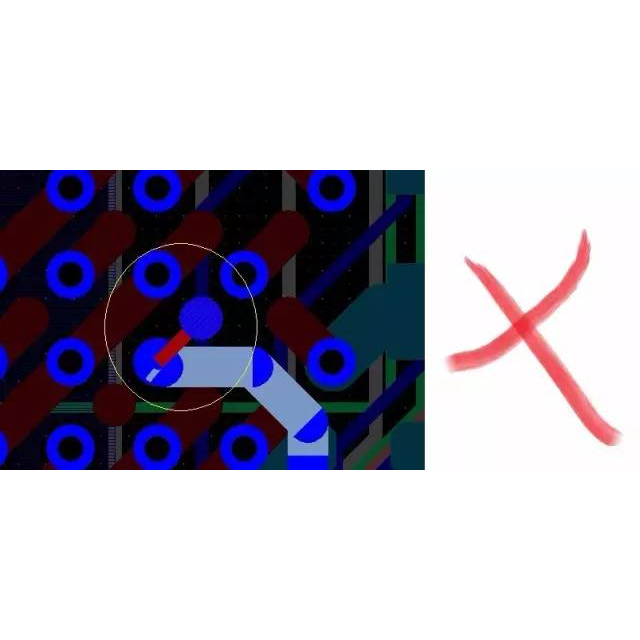

- PCB パッケージの穴が近すぎる

プリント基板の設計、製図、パッケージングでは、ピンホール間の距離に注意する必要があります。たとえベアプレートが生成できたとしても、ピンホール間の距離が狭いため、ウェーブはんだ付けによる組立時に錫ショートが発生しやすくなります。

下図に示すように、ピンの間隔が狭いとショートが発生する可能性があります。はんだ付け錫のショートにはさまざまな原因があります。設計段階で組立性を事前に防ぐことができれば、トラブルの発生を減らすことができます。

- 問題の説明

製品DIPの波頭溶接後、エア溶接に属するネットワークソケットの固定足のはんだ板に重大な錫不足があることが判明しました。

- 問題の影響

その結果、ネットワークソケットとPCBボードの安定性が低下し、製品の使用中に信号ピンフットに力が加わり、最終的には信号ピンフットの接続につながり、製品に影響を与える可能性があります。パフォーマンスが低下し、ユーザーの使用に失敗するリスクを引き起こします。

- 問題の拡張

ネットワークソケットの安定性が悪く、信号ピンの接続パフォーマンスが悪く、品質に問題があるため、ユーザーにセキュリティリスクをもたらす可能性があり、最終的な損失は想像を絶します。

- DIP デバイスのピンに関連する問題は数多くあり、多くの重要なポイントが無視されやすく、最終的には基板がスクラップになってしまいます。では、このような問題を迅速かつ完全に解決するにはどうすればよいでしょうか?

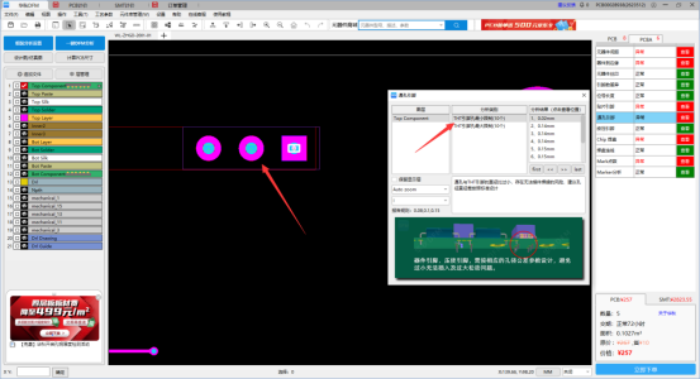

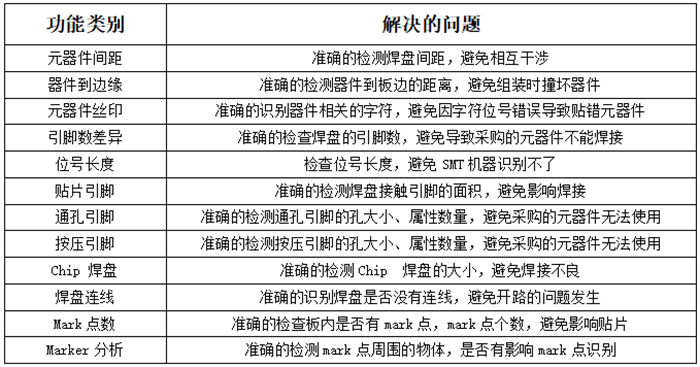

- ここでは、CHIPSTOCK.TOP ソフトウェアのアセンブリおよび分析機能を使用して、DIP デバイスのピンの特別な検査を行うことができます。検査項目には、スルーホールのピン数、THT ピンの大限界、THT ピンの小限界、THT ピンの属性が含まれます。ピンの検査項目は基本的にDIPデバイスの設計上の問題を網羅しています。

- PCB設計の完了後、PCBAアセンブリ解析機能を使用して、設計欠陥を事前に発見し、生産前に設計の異常を解決し、アセンブリプロセスでの設計上の問題、生産時間の遅延、研究開発コストの無駄を回避できます。

- 組立解析機能は、大項目10項目、細項目234項目の検査ルールを備え、デバイス解析、ピン解析、パッド解析など、考えられる組立問題を網羅しており、技術者が事前に予測できないさまざまな生産状況を解決できます。